2014~2020

本研究室の研究に対するモチベーション

現代の情報化社会においてはハイエンドサーバがクラウドという形でITインフラを支え、スマートフォンなどの携帯端末や色々なセンサがエッジデバイスとして価値あるサービスをもたらし私たちの生活をより快適なものにしています。これらの電子機器の中核は高度に集積化された電子回路(集積回路)です。集積回路は極めて沢山のトランジスタとメモリデバイスから構成されています。現在のトランジスタの大きさは20nmよりも小さい驚くべき領域に入っており、1チップ上に集積されるトランジスタの数は微細加工技術の高度な発展により今や数億個にもなります。IoTやAIの時代をむかえ、従来の集積回路技術そしてその基盤となるトランジスタ・メモリ技術に新たな革新が求められています。本研究室では集積回路・システムが新たな価値を創出するために、革新的なナノデバイスとその集積化技術を探求しています。

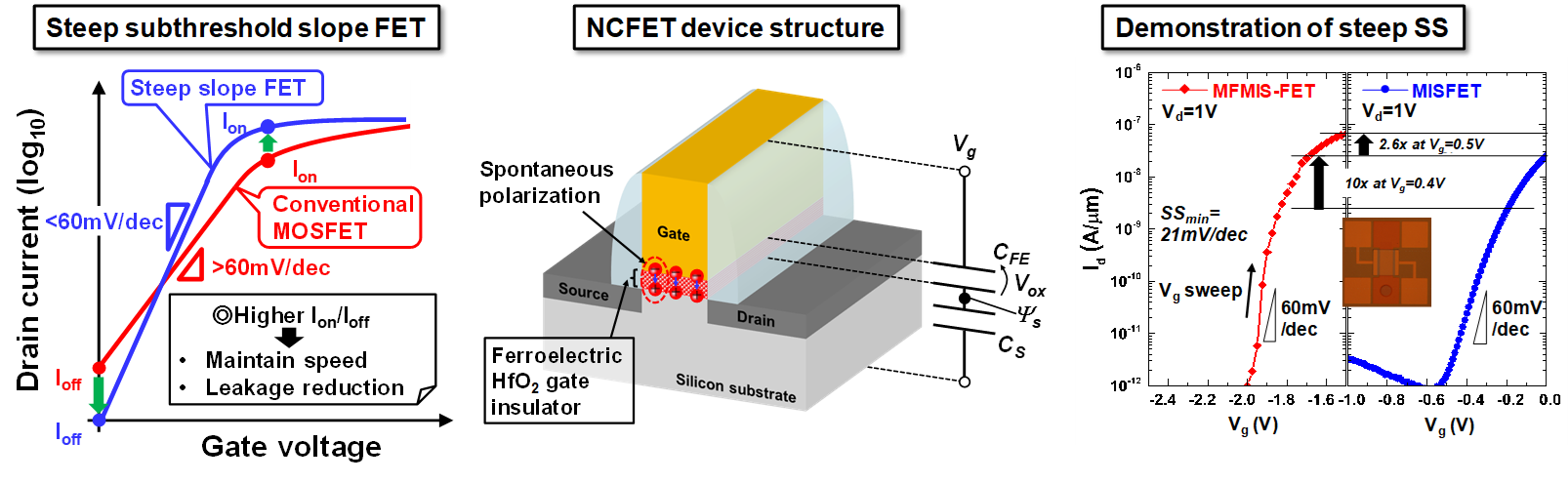

(1) 物理限界を超えた急峻サブスレショルド係数トランジスタ ~負性容量トランジスタ~

集積回路の低消費電力化を実現するにはトランジスタを駆動する電源電圧を下げることが最も効果的です。しかし単純に電源電圧を下げると今度は駆動電流が下がり回路の動作速度が落ちる問題があります。このトレードオフを解決するためにはトランジスタを低い電源電圧でより急峻に立ち上げなければなりません。ところがトランジスタの立ちあがりを決めるサブスレショルド係数には、熱統計物理学で規定される60mV/dec(室温)という物理限界があります。この物理限界を打破するアプローチとして、負性容量トランジスタがあります。負性容量トランジスタ(NCFET)は強誘電体薄膜をゲート絶縁膜とするトランジスタで、実効的にチャネルの表面ポテンシャルを増幅し急峻にトランジスタを立ち上げることができる、大変興味深い技術です。私たちはNCFETのデバイス物理を追求するとともに、の超低電圧動作のための設計指針を提案し、実際デバイス試作により急峻スロープの実現とそのメカニズムの解明に取り組んでいます。

Reference: M. Kobayashi et al., VLSI symposium 2015, K. Jang et al., IEDM 2016, C. Jin et al., IEDM 2018.

(2) 集積回路の超低消費電力化に資するメモリデバイス技術

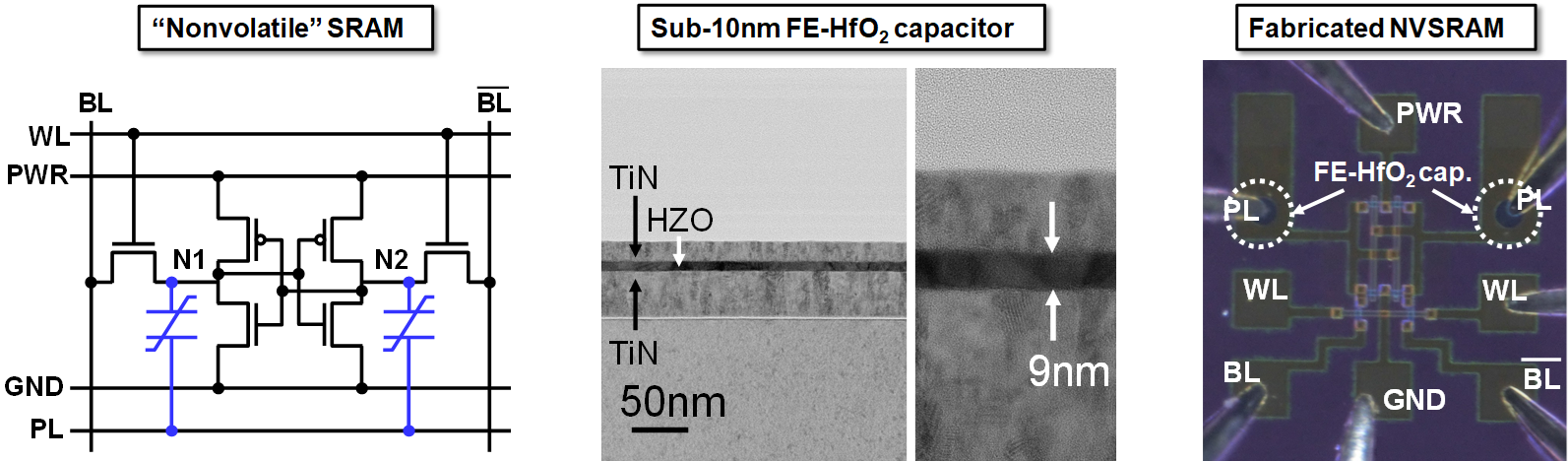

半導体メモリ技術はトランジスタと並んで大変重要な集積デバイス技術です。どんな集積回路もメモリが欠かせません。IoTデバイスは間欠動作しており、ほとんどの時間スリープ状態で、必要な時だけ起動し情報処理と通信を行っています。そのため集積回路の消費電力は待機時のリーク電力が支配的となるため、大容量なメモリデバイスにおけるリーク電流の削減が必須となります。不揮発性メモリは電源をオフにしてもデータをほじできるため、特にIoTデバイスでは重要な役割を果たします。私たちはCMOS集積化プロセスと整合性の高い強誘電体材料を用いた超低消費電力メモリの実用化に向けた研究を行っています。例えば10nm以下の極めて薄い強誘電体HfO2薄膜技術を開発し、そのキャパシタをSRAM上に集積した不揮発性メモリを動作実証しました。この技術はIoTデバイスにおけるローカルな電源管理技術として期待されます。

Reference: M. Kobayashi et al., VLSI symposium 2017.

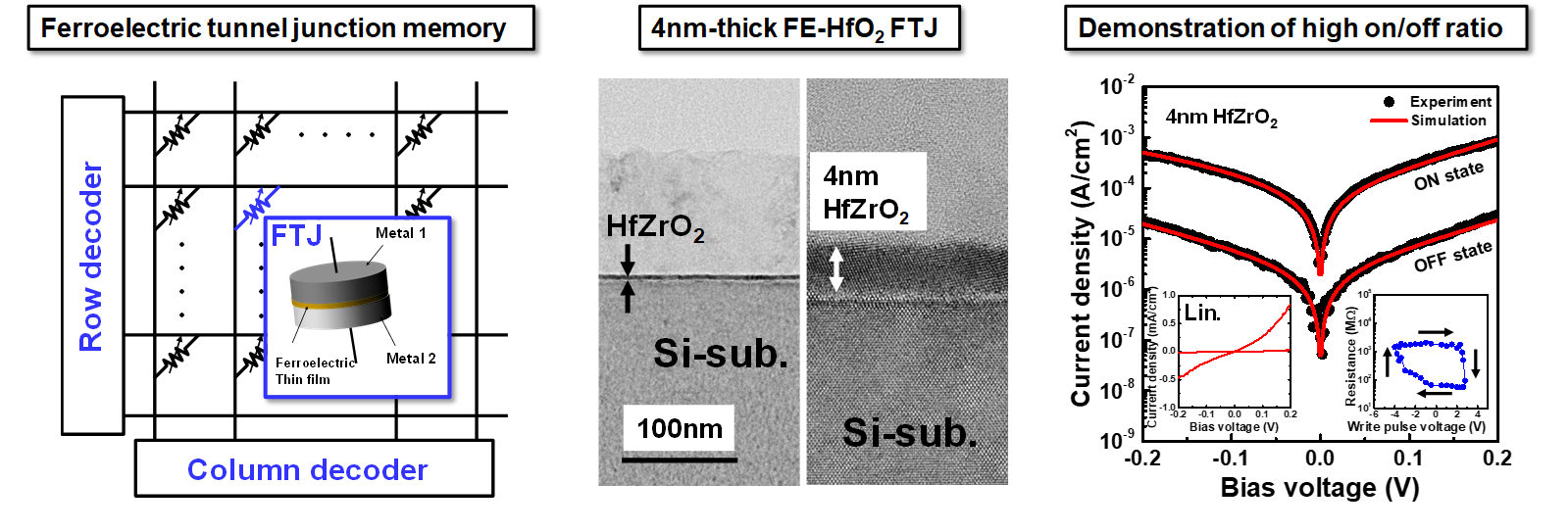

(3)ハードウェア人工知能(AIチップ)実現に向けたデバイス技術

ディープラーニングをはじめとする人工知能技術が学会・産業において大変盛況です。現在これらのアルゴリズムはパワフルなPC・サーバ上でソフトウェアによって実装されています。この手法は容易ではありますが、消費電力が大きいことが問題です。また最近ではクラウドにおける計算・通信の負担が大きいため、IoTのエッジデバイスに人工知能アルゴリズムを搭載したいという要求が高くなっています。そのため人工知能アルゴリズムをエネルギー効率の高いハードウェアで実装し低消費電力化を実現することが望まれています。人工知能アルゴリズムの基本となる人工ニューラルネットワークはもともと人間の脳の働きにインスパイアされており、学習・推論を超並列でエネルギー効率高く行うことができます。ハードウェアで実装するためには神経細胞で中心的な機能をもつニューロンとシナプスを電子デバイスで実装することになります。シナプスにおいてはニューロン間の電気信号のコンダクタンスを保存しておく必要があり、それには不揮発性メモリが適しています。私たちはシナプスデバイスとしてCMOSと整合性の高い強誘電体の薄膜を用いた強誘電体トンネル接合(FTJ)メモリに注目しています。これまでにFTJのデバイス設計指針を打ち立てるとともに、4nmという極薄の強誘電体HfO2でFTJとして電流オンオフ比が100にもなる優れた特性と多値動作を実証してきました。現在、システム・回路・デバイスを統括してハードウェアAIの実現に向けて鋭意研究しています。

Reference: M. Kobayashi et al., Silicon Nano Workshop 2017, F. Mo et al., IEDM 2018.